08擭5寧夵廋偟傑偟偨

夞楬恾偺嵶晹偑尒偊偵偔偄帪偼僽儔僂僓偺昞帵攞棪傪戝偒偔偟偰偛棗壓偝偄

婎斅幨恀傊

丂幚梡壔偺姶憐

丂VFO夞楬恾傊

丂DDS惂屼傊

丂僩僢僾儁乕僕宯摑恾傊

丂H.P僩僢僾傊

丂摉弶偼僾儗儈僢僋僗曽幃偱僗僞乕僩偟傑偟偨丅僗僾儕傾僗傪弌偝側偄傛偆偵丄倁俥俷偲僿僥儘僟僀儞悈徎敪怳婍偺廃攇悢偺揔愗側慻傒崌傢偣傪偝偑偟傑偟偨偑丄偙傟偱傛偟偲偡傞廃攇悢偼悑偵尒偮偗傞偙偲偑弌棃偢丄倁俥俷 12.57MHz偐傜13.57MHz丂僿僥儘僟僀儞悈徎敪怳婍偺廃攇悢28.43MHz偲偟偰俆侽俵俫倸偐傜俆侾俵俫倸傪僇僶乕偟傑偟偨偑丄倁俥俷偺敪怳廃攇悢偑崅偔偰廃攇悢曄摦偑戝偒偄丄壏搙曗惓偑僋儕僠僇儖偱擄偟偄丄梊婜偟側偐偭偨懡偔偺僗僾儕傾僗偺弌尰丄側偳偵擸傑偝傟丄埨掕偵係侾俵俫倸傪捈愙敪怳偝偣傞偟偐夝寛偺曽朄偼側偄偲巚偄帄傝傑偟偨丅

丂係擭屻丂摉帪晛媦偟巒傔偨儌僩儘乕儔幮偺 俬俠 俵俠亅係侽係係 埵憡専弌婍傪巊偭偰係侾俵俫倸揹埑惂屼敪怳婍偺廃攇悢傪惂屼偡傞偙偲偵壜擻惈傪尒弌偟丅帺椼敪怳偺係侾俵俫倸嬊敪傪俁俁俵俫倸戜悈徎敪怳婍偱僟僂儞僐儞僶乕僩偟偰俈俵俫倸戜偵棊偲偟丄俈俵俫倸戜偺埨掕側倁俥俷傪儕僼傽儗儞僗偵偟偰埵憡斾妑偟丄俹俴俴惂屼偟傛偆偲峫偊偮偒傑偟偨丅

丂摉帪儊乕僇乕偺MC-4044偺巊偄曽偼僔儞僙僒僀僓乕曽幃偱丄俰俙俼俴 惂掕偺偺俥俵僠儍儞僱儖僾儔儞偵崌傢偣偰 1 僗僥僢僾 20KHz 丄廬偭偰埵憡斾妑廃攇悢傕20KHz偱偟偨偐傜丄巹偑峫偊偰偄偨7MHz戜偱埵憡専弌婍偑摦嶌偡傞偐偳偆偐媈栤偱偟偨偑丄TTL IC 偑偙偺曈傝偺廃攇悢偱摦嶌偟偰偄傞偺偩偐傜弌棃傞偺偱偼側偄偐偲峫偊丄傗偭偰尒偨偄側偲巚偆傛偆偵側傝傑偟偨丅

丂僼僄乕僘僨僥僋僞乕傪巊偄偙側偡側偳弶傔偰偺偙偲偱丄偙偺偆偊傕側偔摢偺捝偄偙偲偱偟偨偑丄岾塣偵傕嬑柋愭偵丄俠俻帍忋偵俵俠亅係侽係係傪巊梡偟偨俆俵俫倸僔儞僙僒僀僓乕傪敪昞偟偨偽偐傝偺愭払偺俰俙俁俶俤俰徏旜巵偑偄傑偟偨偺偱丄憗懍嫵偊傪惪偄傑偟偨傜 崸愗挌擩偵揱庼偝傟儌僩儘乕儔幮偺塸暥偺儅僯儏傾儖偺僐僺乕傑偱傕傜偄丄傗傔傞栿偵偼偄偐側偄偲偙傠傊捛偄崬傑傟偰偟傑偄傑偟偨丅

幚梡壔偺姶憐 丂丂夞楬恾 丂丂婎斅幨恀 丂丂僩僢僾儁乕僕宯摑恾傊 丂丂VFO夞楬恾傊 丂丂DDS惂屼傊

丂08擭3寧 撍擛 PLL儐僯僢僩偱41MHz偺嬊晹敪怳偑掆巭偟 憲庴晄擻偵側傝傑偟偨丅

屘忈偑敪惗偡傞偲恀偭愭偵媈傢傟傞偺偑僩儔儞僕僗僞偱丄巹傕 偛懡暘偵楻傟偢恀偭愭偵庢傝奜偟僪僕傪偟偰FET 2SK125傪攋懝偝偣偰偟傑偄傑偟偨丅戙昳偲偟偰2SK192傪擖傟偨偺偱偡偑丄夡傟偰傕偄側偄傕偺傪岎姺偟偰傕暅媽偡傞偼偢偼偁傝傑偣傫丅

丂屘忈売強偼僋儔僢僾宆敪怳婍偺僼僀乕僪僶僢僋傪彾偭偰偄傞億儕僗僠儘乕儖僐儞僨儞僒乕(捠徧僗僠僐儞)偺梕検敳偗偱偟偨丅

偙偺儕僌偱僗僠僐儞偺梕検敳偗屘忈偼2搙栚偱丄偦傟埲奜栚棫偭偨屘忈偼婲偒偰偄側偄偺偱僗僠僐儞偼捛曻偡傞帠偵偟丄摨偠偲偙傠偵巊偭偰偄偨傕偆堦偮偺僗僠僐儞傕堦弿偵僨傿僢僾儅僀僇僐儞僨儞僒乕偵岎姺偟傑偟偨丅

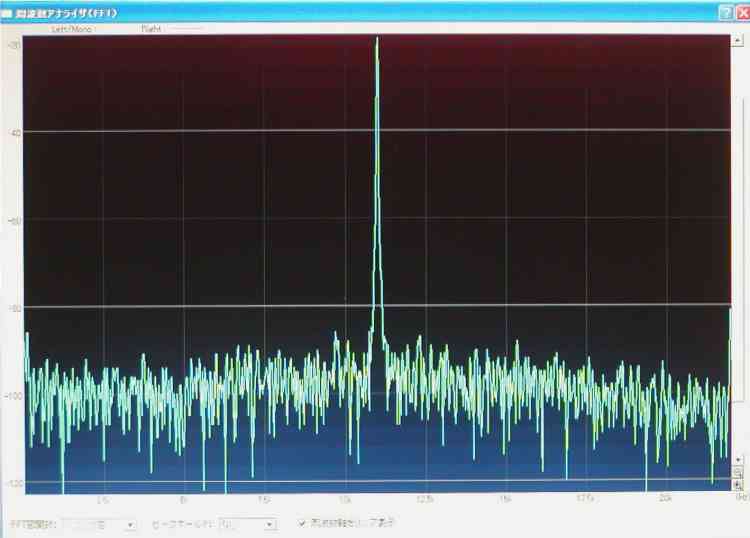

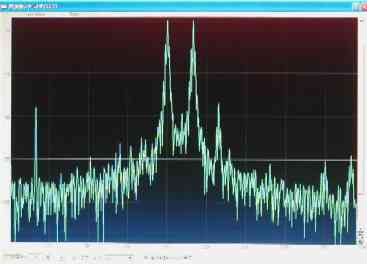

丂暅媽摦嶌妋擣偺偨傔 娙堈僗儁僋僩儖傾僫儔僀僓乕偱娤應偟偨偲偙傠 L.O偺僒僀僪僶儞僪偺悶栰偑偢偄傇傫峀偑偭偰偄偨傝丄C/N斾偑35db(P-P/P-P)掱搙偟偐偁傝傑偣傫丅

僷乕僣傪岎姺偟偨傜摦嶌忦審傕曄傢偭偨條偱丄擺摼偺弌棃傞摦嶌傪偡傞條偵側傞傑偱 偢偄傇傫偺帋峴嶖岆傪偡傞塇栚偵側傝傑偟偨丅

丂曄峏偺撪梕偼埲壓偺婰帠偺拞傊捛婰偡傞偙偲偵偟傑偡丅

丂俹俴俴偼宯偑儖乕僾偵側偭偰偄傑偡偐傜丄埨掕偵摦嶌偝偣傞偵偼丄棟榑偵偦偭偨夁搉墳摎摦嶌傪偝偣傞傛偆偵儖乕僾僼傿儖僞乕偺夞楬掕悢傪寛掕偟側偗傟偽側傝傑偣傫丅

丂儌僩儘乕儔偺儅僯儏傾儖偼巹偺摢偱偼偳偆偵傕側傜側偄棟榑幃傪夝愢偟偰丄彅掕悢傪寛掕偡傞寁嶼幃傪柧帵偟偰偁傝傑偟偨偺偱偨偄傊傫偵彆偐傝傑偟偨丅

徻嵶傪徣棯偟偰嵟廔偺寁嶼幃偩偗傪偙偙偵暲傋偰偍偒傑偡丅

R1=俲冇俲倴乛N冎n2C丂R2=2兡乛冎nC(儅僯儏傾儖偺儈僗偱兡偑敳偗偰偄傑偟偨)丂C=俲冇俲倴乛N冎n2R1

08擭5寧 捛婰

丂N偼VCO偺廃攇悢傪儗僼傽儗儞僗廃攇悢傑偱暘廃偟偰壓偘傞帪偺暘廃斾偱偡丅摉弶 杮婡偱偼僿僥儘僟僀儞曽幃偱廃攇悢曄姺偟偰偄傞偐傜 N 偺悢抣偼昁梫側偄偲峫偊擖傟偰偄傑偣傫偱偟偨偑丄崱夞峫偊捈偟 N=41MHz/7.15MHz=5.7偲塢偆偙偲偵偟偰帪掕悢偺寁嶼偺拞偵擖傟傑偟偨丅

埲壓丂儅僯儏傾儖偵廬偭偰俹俴俴儖乕僾偺彅掕悢傪師偺條偵寛傔傑偟偨丅

仺 婰崋偺偆偟傠偼曄峏偟偨偲偙傠偱偡丅

侾師儔僌儕乕僪宆俴俹俥偺夁搉墳摎嬋慄偐傜

兡乮僟儞僺儞僌僼傽僋僞乕乯傪 0.8偵慖傇偲冎nt偼 4.5 仺 0.5偵慖傇偲冎nt偼 4.2

t乮儘僢僋僀儞僞僀儉乯傪 0.001sec偵寛傔傞偲 仺 0.02sec偵寛傔傞偲

冎n乮儖乕僾偺帺慠廃攇悢乯偼 4.5x103rad/sec 仺 2.15x102rad/sec

俲冇乮埵憡斾妑婍偺姶搙乯儌僩儘乕儔偺僨乕僞乕偐傜 0.12volt/rad

丂係侾俵俫倸倁俠俷偺曄挷姶搙乮俲倴乯偼俹俴俴儖乕僾偺摿惈傪寛傔傞廳梫側忦審偵側傞偺偱丄幹偺栚婎斅忋偵僶儔僢僋寢慄偟偰丄僶儕僉儍僢僾偺報壛揹埑傪俀倁曄壔偝偣偨偲偒係侾俵俫倸偐傜係俀俵俫倸傪敪怳偡傞傛偆偵敪怳婍偺彅掕悢傪寛傔傑偟偨丅係俀俵俫倸敪怳帪僉儍僾僠儍乕儗儞僕偑嫹偔側傜側偄傛偆偵報壛揹埑傪崅傔偵偟傑偟偨丅

丂丂丂丂丂丂丂丂丂丂丂俲v=2兾x廃攇悢曄壔(42-41MHz=1MHz)乛揹埑曄壔(2V)

丂丂丂丂丂丂丂 丂丂丂丂丂=3.14倶106丂丂rad/sec/volt

丂忋婰偺愝掕偐傜儖乕僾僼傿儖僞乕偺彅掕悢傪儅僯儏傾儖偺寁嶼幃偳偍傝寛掕偟傑偟偨丅

丂丂丂丂丂丂丂丂俠傪壖掕偟偰丂丂丂丂丂丂丂1兪F 仺 6.8兪F

丂丂丂丂丂丂丂丂俼俀丂丂丂丂丂丂丂丂丂丂丂350ohm 仺 680ohm

丂丂丂丂丂丂丂丂俼侾丂丂丂丂丂丂丂丂丂丂丂18.6K 仺 220K

丂俼侾傪5Kohm埲忋偺抣偱巊偆偲偒丄儌僩儘乕儔幮偼俬俠偺摦嶌傪忦審偮偒偱偟偐曐徹偟偰偄傑偣傫丅

丂棟桼偼俬俠偵慻傒崬傑傟偰偄傞傾僋僥傿僽僼傿儖僞梡傾儞僾偺擖椡掞峈偑掅偄偺偱丄俼侾偺掞峈抣偑崅偔側傞偲丄傾儞僾偺僶僀傾僗揹棳偑晄揔摉偵側傞丆僎僀儞偑掅壓偟偰儖乕僾僼僀儖僞偑愝寁捠傝偵側傜側偄丆儖乕僾僎僀儞傕壓偑偭偰偟傑偭偰僒僀僪僶儞僪僲僀僘偺憹壛傗埵憡専弌岆嵎偑憹壛偡傞丆摍乆偵側傞偺偩偦偆偱偡丅

丂懳嶔偵偼慜抜偵僄儈僢僞僼僅儘儚偐僜乕僗僼僅儘儚傪捛壛偡傞偙偲傪悇彠偟偰偄傑偡丅

巹偼俬俠撪憻偺傾儞僾傪巊傢偢丄暿偺俿俼傪奜晅偗偵偟傑偟偨丅 仺 崱夞偺夵廋偱峏偵MOS FET 2SK241偺僜乕僗僼僅儘儚偵曄峏偟傑偟偨丅

丂傑偨僉儍僾僠儍乕儗儞僕偑嫹偔側傜側偄條偵傾僋僥傿僽僼傿儖僞乕偺揹尮傪12V偵偟偰偄傑偡丅

夞楬恾傊 丂丂婎斅幨恀傊 丂丂僩僢僾儁乕僕宯摑恾傊 丂丂VFO夞楬恾傊 丂丂DDS惂屼傊

丂08擭8寧捛婰

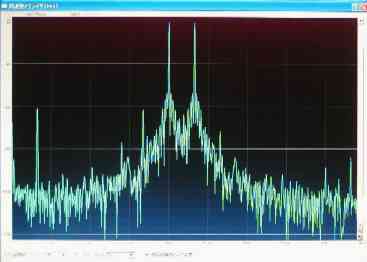

丂廋棟傪廔偊偰嵟廔妋擣傪偡傋偔丄Mixer儐僯僢僩弌椡傪娙堈僗儁僋僩儖傾僫儔僀僓乕偱娤應偟偨偲偙傠丄婜懸偟偰偄偨攇宍偲偼掱墦偔悶栰偺峀偑偭偨攇宍傪栚偵偟偰價僢僋儕偟傑偟偨丅

丂尨場偲偟偰嵟弶偵巚偄晜偐傫偩帠偼丄PLL偑晄揔愗側摦嶌傪偟偰偄傞偺偱偼側偄偐偲塢偆偙偲偱偟偨丅

幚偼巹丂偙偺儕僌傪挿婜娫幚梡偟偰偄傞娫偵丄PLL偵娭偡傞暥專傪撉傫偱儘僢僋僀儞僞僀儉偑杮婡偼摉弶1ms偲偟偰偄傑偟偨偑丄悽娫偺捠怣婡偼10ms偵側偭偰偄傞傕偺偑懡偄偙偲偑婥偵側偭偰偄傑偟偨丅

丂摦嶌晄挷偵側傞偲傗偼傝恀偭愭偵偙偺偙偲偵堷偭妡偐傝丄堦搙傗傝捈偟偰傒傛偆偲巚偄棫偪傑偟偨丅

丂儌僩儘乕儔幮偺MC4044偺儅僯儏傾儖傪撉傒捈偟丄儘僢僋僀儞僞僀儉10ms偵偟偰丄C傪6.8兪F偲壖掕偟丄R1,R2傪寁嶼偟捈偟丄婜懸偟偰摦嶌偝偣偰尒傑偟偨偑丄彮偟椙偔側偭偨掱搙偱NG偱偟偨丅

偝傜偵20ms偱偼擛壗偲傗偭偰尒傑偟偨偑丄傑偨彮偟椙偔側偭偨偐側偲巚偆掱搙偱NG偱偟偨丅

偦傟偱傕儘僢僋僀儞僞僀儉偼挿偔偟偰傕埆偔偼側傜側偄條巕偱偡偟丄尦偵栠偡偺偼柺搢側偺偱20ms偺傑傑偵偟傑偟偨丅

丂儘僢僋僀儞僞僀儉偑挿偄偲僷儚乕僆儞偟偨帪側偳偼丄儘僢僋僀儞偡傞傑偱10昩埵妡偐傝婥帩偪岲偔偁傝傑偣傫丅

懍偔僟僀儎儖傪夢偟偨偖傜偄偱偼暘傜側偄偺偱偦偺傑傑巊偭偰偄傑偡偑丄僉儍僾僠儍乕儗儞僕偑嫹偔側偭偰偟傑偄傑偟偨丅

丂偦傟偱偼壗偑偄偗側偄偺偩傠偆丠偲峫偊丄VCO偺敪怳攇宍偑埆偄偺偱偼丠偲巚偄帄傝傑偟偨丅

丂DC揑側摦嶌傪挷傋傞偲丄Id偑懡偄栚偵棳傟FET偺僪儗儞,僜乕僗娫偵妡偐傞DC揹埑偑掅偔側偭偰偄傞偺偵婥晅偒僜乕僗掞峈傪掅偔偟傑偟偨偑娭學側偟偱偟偨丅

丂僶儕僉儍僢僾偵妡偐傞RF揹埑偑僶僀傾僗揹埑傪墇偊傞偲敪怳攇宍偑埆偔側傞偺偐丠偲峫偊丄僶僀傾僗揹埑傪崅偔偟偰傗偭偰尒傑偟偨偑尠挊偵塭嬁偟傑偣傫偱偟偨丅

丂僼傿乕僪僶僢僋偑嫮偔妡偐傝夁偓偰夁敪怳偟偰偄傞偺偱偼丠偲峫偊偮偒丄僎乕僩,僜乕僗,僌儔儞僪娫偵擖偭偰僼傿乕僪僶僢僋検傪寛傔偰偄傞丄屘忈尨場偵傕側偭偨僐儞僨儞僒乕偺梕検斾傪庬乆曄偊偰尒傑偟偨丅(埲慜偼47PF偱偟偨丅)

丂旝柇偱僋儕僠僇儖偵怓乆僇僢僩傾儞僪僩儔僀偟偰椙偔側傞強傪尒偮偗傞偙偲偑弌棃傑偟偨丅

偙偺挷惍偼 L 偺旝挷惍傕昁梫偵側傝傑偡偐傜戝曄嬯偟偄嶌嬈偱偡丅

嵟屻傑偱庤傪偮偗側偐偭偨棟桼偱傕偁傝傑偡丅

丂椙偔側偭偨 偲偼尵偊僇儞儁僉偲傑偱偼塢偊側偄傕偺偱偟偨偑丄僋儕傾乕側儗儀儖偼50db埲忋妋曐弌棃偰崱枠傛傝20db偼夵慞偟偰偄傞偺偱乽傑偁傛偄偐乿偲懨嫤偟偨巚偄偱偟偨丅

丂偙偙傑偱偼 儐僯僢僩傪働乕僗偺奜偵弌偟偰杮懱偐傜攝慄傪墑挿偟偰偮側偓丄偄傢備傞僶儔僢僋偱摦嶌偝偣偰偄傑偟偨丅

丂働乕僗偵栠偟偰堦廡娫偑宱夁偟丄嵞傃娙堈僗儁僋僩儖傾僫儔僀僓乕偱摦嶌傪妋擣偟傑偟偨傜丄側傫偲偒傟偄側僗儁僋僩儖偵側偭偰偄傞偱偼偁傝傑偣傫偐両両

丂峫偊偰傒傞偲僶儔僢僋偱摦嶌偝偣偰偄傞娫偼丄敿揷晅偗偱晹昳偺庢傝晅偗庢傝奜偟傪昿斏偵傗偭偨偙偲偱丄VCO偵偼旕忢側婡夿揑僗僩儗僗偑妡偐偭偰棊拝偗偢丄僲僀僘偑敪惗偟偰僗儁僋僩儖傪埆偔偟偰偄偨偲悇掕偱偒傑偡丅

丂傕偆堦偮峫偊偮偄偨偙偲偑偁傝傑偡丅傛偔尵傢傟傞偙偲偱偡偑乽PLL惂屼敪怳婍偼僲僀僘偺敪惗偑懡偔僗儁僋僩儖偺悶栰偑峀偑偭偰偒傟偄偱側偄乿偲尵偆偙偲偱偡丅

丂偗傟偳傕 VCO 偑廃攇悢偑埨掕偐偮偒傟偄側攇宍偱敪怳偡傞側傜丄PLL偑娭梌偡傞偲偙傠偑彮側偔丄儘僢僋僀儞僞僀儉偑1ms偱偁傠偆偲20ms偱偁傠偆偲偦傟偼奜晹偐傜惂屼偡傞嵺偺僗僥僢僾墳摎偵堘偄偑弌傞偩偗偱丄柍慄捠怣偵偼偨偄偟偰娭學側偄偙偲偱偡丅

丂6m僶儞僪傗HF僶儞僪偱偼崅惈擻側VCO偑斾妑揑梕堈偵惢嶌壜擻偱偡偐傜丄PLL偺巊梡偵娭偟偰怱攝偼柍梡偲峫偊傑偡丅

Local OSC 偑偒傟偄側攇宍偱側偄応崌偺儈僋僒乕儐僯僢僩偺2怣崋弌椡僗儁僋僩儖

丂丂丂丂丂丂C/N斾偑廩暘偲傟側偄応崌丂丂丂丂丂丂丂丂丂丂丂C/N斾偑旕忢偵埆偄応崌

丂壗偲尵偭偰傕僗僾儕傾僗偑側偄偺偼婥帩偺傛偄傕偺偱偡丅

奆柍偱偼偁傝傑偣傫偑丂傾儞僥僫傪愙偖偲奜棃僲僀僘偵儅僗僋偝傟偰偟傑偆偺偱丄俆侽偐傜俆侾俵俫倸傑偱偺娫偱偦傟偲傢偐傞傕偺偼50.2195MHz偲50.5194MHz偺俀偮偩偗偱偡丅拲堄偟偰扵偭偰傗偭偲敾傞掱搙偱偡丅

丂傾儞僥僫傪僟儈乕掞峈偵懼偊偨帪偵尒偮偗傜傟傞 50偐傜51MHz庴怣帪偺僗僾儕傾僗偼師偺捠傝偱偡丅

丂旕忢偵庛偔S儊乕僞乕偺怳傜側偄傕偺

丂丂丂丂丂丂丂丂丂丂丂丂丂50.0695MHz,50.1871MHz,50.7459MHz,50.8717MHz,50.9516MHz

丂俽儊乕僞乕偑丂0.5怳傞傕偺 丂 丂50.2195MHz

丂俽儊乕僞乕偑丂 1 怳傞傕偺丂丂丂50.5194MHz

丂巹偺庴怣婡偼俽侾偱亅10DB兪V,俽俋偱亄10DB兪V偵側偭偰偄傑偡丅

丂僗僾儕傾僗偼壗攞偐偺崅挷攇摨巑偑價乕僩偵側偭偰僶儞僪撪偵棊偪崬傫偱偔傞偺偱丄

丂掅儗儀儖偱丄偟偐傕崅挷攇偱偡偐傜彮偟廃攇悢傪偢傜偡偲媫偵栚揑怣崋偐傜棧傟偰偄偒傑偡偐傜丄

丂偦傟傎偳巟忈偵偼側傝傑偣傫丅

丂庴怣婡偵旘傃崬傓応強偼傾儞僥僫攝慄偐傜偱偡丅

丂係侾俵俫倸嬊敪偵偼崅挷攇埲奜偺晄弮側惉暘偼擖偭偰偄側偄條巕偱偡丅